Transistor And Gate Sizing . Best case pull up resistance: eff= β(1/3 +1/6) = 2 x (1/2) = 1. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. the sizing of the transistor can be done using rc delay approximation. Calculate total capacitance driven by the gates in the circuit. Estimate the percentage of the devices operating at the max clock. The rc delay model helps in delay estimation cmos circuit. consider the following simplifications: Sizing of transistors to balance performance of single inverter.

from www.slideserve.com

the sizing of the transistor can be done using rc delay approximation. Estimate the percentage of the devices operating at the max clock. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. consider the following simplifications: eff= β(1/3 +1/6) = 2 x (1/2) = 1. Sizing of transistors to balance performance of single inverter. Best case pull up resistance: The rc delay model helps in delay estimation cmos circuit. Calculate total capacitance driven by the gates in the circuit.

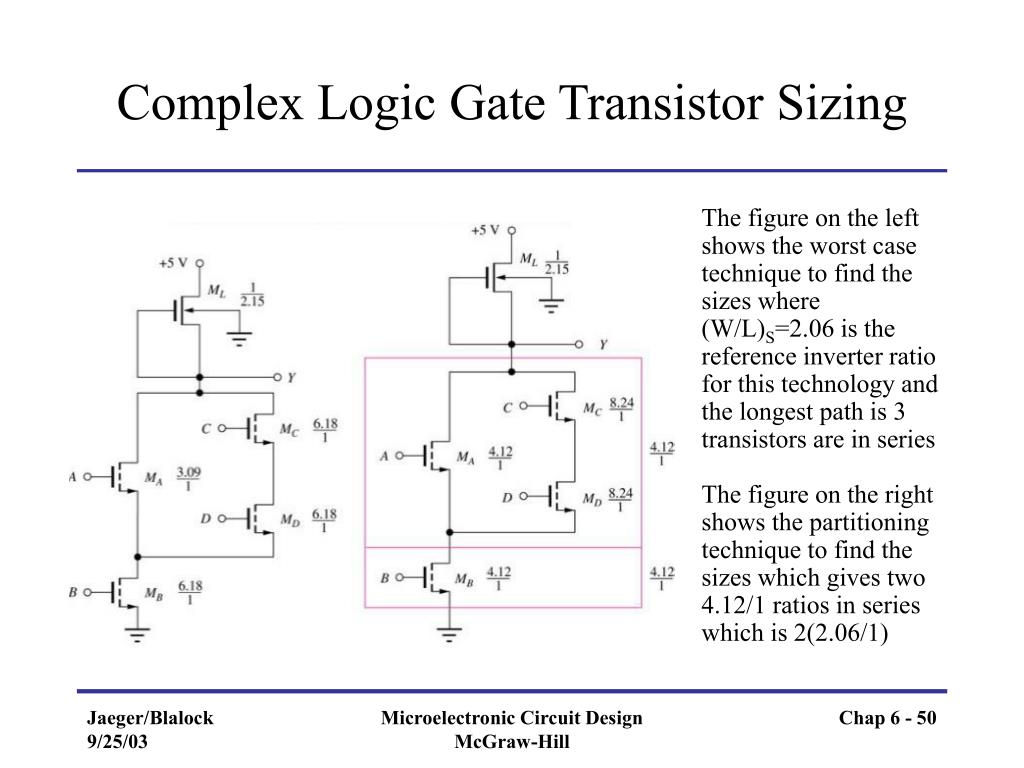

PPT Chapter 6 Introduction to Digital Electronics PowerPoint Presentation ID5753557

Transistor And Gate Sizing Calculate total capacitance driven by the gates in the circuit. the sizing of the transistor can be done using rc delay approximation. Estimate the percentage of the devices operating at the max clock. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Calculate total capacitance driven by the gates in the circuit. The rc delay model helps in delay estimation cmos circuit. Sizing of transistors to balance performance of single inverter. eff= β(1/3 +1/6) = 2 x (1/2) = 1. consider the following simplifications: Best case pull up resistance:

From www.researchgate.net

A standard digital CMOS NAND3 gate and its internal transistor schematic. Download Scientific Transistor And Gate Sizing consider the following simplifications: Best case pull up resistance: Sizing of transistors to balance performance of single inverter. Calculate total capacitance driven by the gates in the circuit. the sizing of the transistor can be done using rc delay approximation. The rc delay model helps in delay estimation cmos circuit. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] =. Transistor And Gate Sizing.

From www.scribd.com

Design and Sizing of Various CMOS Logic Gates for Specific Transistor Technology Parameters and Transistor And Gate Sizing Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Sizing of transistors to balance performance of single inverter. eff= β(1/3 +1/6) = 2 x (1/2) = 1. Best case pull up resistance: The rc delay model helps in delay estimation cmos circuit. the sizing of the transistor can be done using rc delay approximation.. Transistor And Gate Sizing.

From www.chegg.com

Solved Problem 3 Transistor Sizing and Gate Delay (a) Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. eff= β(1/3 +1/6) = 2 x (1/2) = 1. consider the following simplifications: the sizing of the transistor can be done using rc delay approximation. Sizing of transistors to balance performance of single inverter. The rc delay model helps in delay estimation cmos circuit. Calculate total. Transistor And Gate Sizing.

From www.youtube.com

CMOS Logic Design Transistor Sizing YouTube Transistor And Gate Sizing eff= β(1/3 +1/6) = 2 x (1/2) = 1. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Best case pull up resistance: consider the following simplifications: Estimate the percentage of the devices operating at the max clock. The rc delay model helps in delay estimation cmos circuit. Calculate total capacitance driven by the. Transistor And Gate Sizing.

From www.semanticscholar.org

Figure 2 from A gate sizing and transistor fingering strategy for subthreshold CMOS circuits Transistor And Gate Sizing the sizing of the transistor can be done using rc delay approximation. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. The rc delay model helps in delay estimation cmos circuit. consider the following simplifications: Best case pull up resistance: eff= β(1/3 +1/6) = 2 x (1/2) = 1. Sizing of transistors to. Transistor And Gate Sizing.

From itecnotes.com

Electrical Sizing transistors for a CMOS circuit Valuable Tech Notes Transistor And Gate Sizing Best case pull up resistance: The rc delay model helps in delay estimation cmos circuit. Calculate total capacitance driven by the gates in the circuit. the sizing of the transistor can be done using rc delay approximation. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. eff= β(1/3 +1/6) = 2 x (1/2) =. Transistor And Gate Sizing.

From partdiagramkastamidp.z21.web.core.windows.net

And Gate Circuit Diagram Using Transistor Transistor And Gate Sizing the sizing of the transistor can be done using rc delay approximation. Sizing of transistors to balance performance of single inverter. Calculate total capacitance driven by the gates in the circuit. The rc delay model helps in delay estimation cmos circuit. consider the following simplifications: Best case pull up resistance: Eff= β[((1/6 +1/6) || (1/3)) + 1/6] =. Transistor And Gate Sizing.

From www.youtube.com

Transistor AND Gate YouTube Transistor And Gate Sizing Sizing of transistors to balance performance of single inverter. Best case pull up resistance: the sizing of the transistor can be done using rc delay approximation. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Calculate total capacitance driven by the gates in the circuit. The rc delay model helps in delay estimation cmos circuit.. Transistor And Gate Sizing.

From www.chegg.com

1. Transistor Models and Gate Sizing a) If sized Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. The rc delay model helps in delay estimation cmos circuit. Sizing of transistors to balance performance of single inverter. eff= β(1/3 +1/6) = 2 x (1/2) = 1. consider the following simplifications: Best case. Transistor And Gate Sizing.

From www.chegg.com

Solved Problem 3 Transistor Sizing and Gate Delay (a) Transistor And Gate Sizing Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. the sizing of the transistor can be done using rc delay approximation. Best case pull up resistance: Calculate total capacitance driven by the gates in the circuit. Sizing of transistors to balance performance of single inverter. The rc delay model helps in delay estimation cmos circuit.. Transistor And Gate Sizing.

From www.chegg.com

Solved (3) [Transistor sizing, 10 pointsl The following Transistor And Gate Sizing Sizing of transistors to balance performance of single inverter. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Estimate the percentage of the devices operating at the max clock. The rc delay model helps in delay estimation cmos circuit. the sizing of the transistor can be done using rc delay approximation. Best case pull up. Transistor And Gate Sizing.

From www.slideserve.com

PPT COMBINATIONAL LOGIC PowerPoint Presentation, free download ID6637108 Transistor And Gate Sizing Calculate total capacitance driven by the gates in the circuit. Sizing of transistors to balance performance of single inverter. Best case pull up resistance: the sizing of the transistor can be done using rc delay approximation. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Estimate the percentage of the devices operating at the max. Transistor And Gate Sizing.

From www.176iot.com

and gate transistor diagram IOT Wiring Diagram Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. consider the following simplifications: Sizing of transistors to balance performance of single inverter. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. eff= β(1/3 +1/6) = 2 x (1/2) = 1. the sizing of the transistor can be done using rc delay. Transistor And Gate Sizing.

From www.engineersgarage.com

AND Gate using Transistor EngineersGarage Transistor And Gate Sizing The rc delay model helps in delay estimation cmos circuit. Calculate total capacitance driven by the gates in the circuit. Best case pull up resistance: Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. eff= β(1/3 +1/6) = 2 x (1/2) = 1. consider the following simplifications: Estimate the percentage of the devices operating. Transistor And Gate Sizing.

From www.chegg.com

Solved Problem 3 Transistor Sizing and Gate Delay (a) Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. eff= β(1/3 +1/6) = 2 x (1/2) = 1. The rc delay model helps in delay estimation cmos circuit. Calculate total capacitance driven by the gates in the circuit. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Sizing of transistors to balance performance. Transistor And Gate Sizing.

From www.electroniclinic.com

Logic Gates in Digital Electronics Complete Guide Electronic Clinic Transistor And Gate Sizing Best case pull up resistance: eff= β(1/3 +1/6) = 2 x (1/2) = 1. consider the following simplifications: Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. Calculate total capacitance driven by the gates in the circuit. The rc delay model helps in delay estimation cmos circuit. Sizing of transistors to balance performance of. Transistor And Gate Sizing.

From www.youtube.com

Transistor Logic Gates NAND, AND, OR, NOR YouTube Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. eff= β(1/3 +1/6) = 2 x (1/2) = 1. The rc delay model helps in delay estimation cmos circuit. Eff= β[((1/6 +1/6) || (1/3)) + 1/6] = β[1/6 + 1/6] = 1/3. the sizing of the transistor can be done using rc delay approximation. Sizing of transistors. Transistor And Gate Sizing.

From www.slideserve.com

PPT Chapter 6 Introduction to Digital Electronics PowerPoint Presentation ID5753557 Transistor And Gate Sizing Estimate the percentage of the devices operating at the max clock. Sizing of transistors to balance performance of single inverter. Best case pull up resistance: the sizing of the transistor can be done using rc delay approximation. eff= β(1/3 +1/6) = 2 x (1/2) = 1. Calculate total capacitance driven by the gates in the circuit. The rc. Transistor And Gate Sizing.